جزییات برنامه TSMC برای ساخت چیپست با لیتوگرافی 3 نانومتری

نمایش خبر

| تاریخ : 1399/6/6 نویسنده: مسعود بهرامی شرق | ||

| برچسبها : | تی اس ام سی TSMC | |

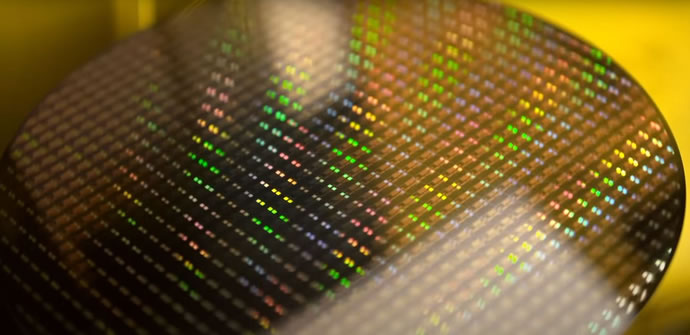

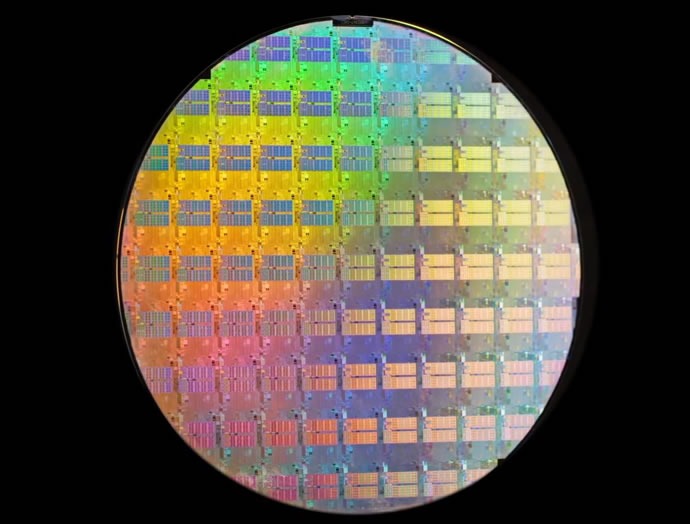

پس از +N7 (که برای نمونه در تولید چیپستهای Kirin 990 مورد استفاده قرار گرفت)، N5 دومین نسل از لیتوگرافیهای DUV و EUV به شمار میرود. ساخت تراشه با این لیتوگرافی چند ماهیست که در TSMC به مرحله تولید انبوه رسیده و انتظار میرود نسل بعدی چیپستهای اپل (برای استفاده در آیفون 12) با همین لیتوگرافی ساخته شده باشد. پروسه N5 در مقایسه با N7، تا 15 درصد عملکرد را بهبود بخشیده و میزان مصرف آن نیز تا 30 درصد کمتر خواهد بود. در تکمیل لیتوگرافی N5، کمپانی TSMC پروسه جدیدی به نام N5P را نیز بر مبنای همان پروسه N5 آمادهسازی نموده که ضمن افزایش 5 درصدی سرعت، میزان مصرف آن نیز تا 10 درصد کاهش پیدا کرده است.

دستاورد بعدی TSMC، پروسه تولید 4 نانومتری یا N4 است که با به کارگیری لایههای بیشتری از EUV، پروسه N5 را به تکامل میرساند. نکته مثبت در آنجاست که طراحان چیپست نیز برای مهاجرت از N5 به N4، کار چندان سختی را پیش رو نخواهند داشت. risk production یا تولید مخاطرهآمیز با این پروسه از سهماهه پایانی سال 2021 آغاز خواهد شد و تولید رسمی تراشه با این لیتوگرافی برای سال 2022 پیشبینی شده است. لازم به ذکر است، risk production تولید نخستین سری از تراشهها با یک لیتوگرافی جدید است که البته هیچ کمپانی طراح چیپستی آن را سفارش نداده و بیشتر جنبه پایلوت دارد.

اما همان طور که گفته شد، مهمترین خبر TSMC در این سمپوزیوم، توسعه لیتوگرافی 3 نانومتری یا N3 است. لیتوگرافی 3 نانومتری سامسونگ از ساختارهای ترانزیستوری GAA بهره میبرد، اما TSMC تصمیم گرفته لیتوگرافی 3 نانومتری خود را همچنان با ترانزیستورهای FinFET توسعه دهد. در مقایسه با N5، پروسه N3 میتواند در همان سطح از مصرف، عملکرد را 10 تا 15 درصد افزایش داده و یا با همان سرعت ترانزیستور، میزان مصرف را بین 25 تا 30 درصد کاهش دهد. مقیاس تراکم ناحیه منطق (logic area) نیز 1.7 برابر عنوان شده و این بدان معناست که تراشه ساخته شده با پروسه N3 از لحاظ اندازه باید 0.58 برابرِ تراشه تولید شده با پروسه N5 باشد.

البته این کوچک شدن لزوما به معنی کاهش اندازه در همه ساختارها نیست، زیرا تمام اجزا میتوانند این مسیر ریاضی را طی کرده و در عین حال، عملکرد تراشه را در بهترین حالت خود حفظ کنند. پس از شروع risk production در سال 2021، کمپانی TSMC تولید رسمی تراشه با پروسه 3 نانومتری را از نیمه دوم سال 2022 آغاز خواهد کرد. این در حالیست که نخستین چیپستهای 3 نانومتری سامسونگ در سال 2021 وارد بازار خواهند شد.

در پایان گفتنیست، با توجه به تلاش TSMC برای عبور از لیتوگرافی 3 نانومتری، ممکن است این شرکت در تولیدات خود به مادهای غیر از سیلیکون نیز روی بیاورد. با وجود آنکه هنوز هیچ برنامه مشخصی از سوی TSMC اعلام نشده، این شرکت از تکنولوژیهایی مثل ورقههای نانو (nanosheets) و سیمهای نانو (nanowires) نام برده و اعلام کرده موادی در اختیار دارد که عبور از ضخامت 1 نانومتری را نیز امکانپذیر میکنند. البته این برنامهها برای آینده نزدیک نبوده و تا تحقق آنها فاصله زیادی داریم.

-

معرفی اییربادهای سامسونگ Galaxy Buds4 و Buds4 Pro با طراحی بهبودیافته و ارتقاء قابلیتهای صوتی

معرفی اییربادهای سامسونگ Galaxy Buds4 و Buds4 Pro با طراحی بهبودیافته و ارتقاء قابلیتهای صوتی

-

معرفی سامسونگ Galaxy S26 Ultra کپی برابر اصل S25 Ultra با لنزهای سریعتر و شارژ 60 واتی

معرفی سامسونگ Galaxy S26 Ultra کپی برابر اصل S25 Ultra با لنزهای سریعتر و شارژ 60 واتی

-

معرفی سامسونگ Galaxy S26 و +Galaxy S26 با تغییرات حداقلی و بازگشت Exynos

معرفی سامسونگ Galaxy S26 و +Galaxy S26 با تغییرات حداقلی و بازگشت Exynos

-

رونمایی از iQOO 15R – شبهپرچمداری با Snapdragon 8 Gen 5 و باتری 7,600 میلیآمپر ساعتی

رونمایی از iQOO 15R – شبهپرچمداری با Snapdragon 8 Gen 5 و باتری 7,600 میلیآمپر ساعتی

-

معرفی Oppo A6i+ ،Oppo A6s ،Oppo A6 و Oppo A6v – علاقه عجیب اوپو به سری A6 و بازی با کلمات

معرفی Oppo A6i+ ،Oppo A6s ،Oppo A6 و Oppo A6v – علاقه عجیب اوپو به سری A6 و بازی با کلمات

-

معرفی Band 11 و Band 11 Pro – بندهای تناسب اندام سبک، مقاوم و خوشقیمت هواوی

معرفی Band 11 و Band 11 Pro – بندهای تناسب اندام سبک، مقاوم و خوشقیمت هواوی

-

معرفی ساعت هوشمند Amazfit T-Rex Ultra 2 با دوام باتری 30 روزه و 6 موقعیتیاب ماهوارهای

معرفی ساعت هوشمند Amazfit T-Rex Ultra 2 با دوام باتری 30 روزه و 6 موقعیتیاب ماهوارهای